Interconnection

Network

Interconnection

Network

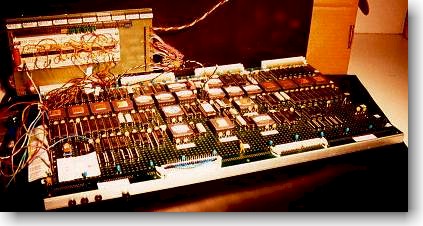

The Multiplus multistage interconnection network is an inverted n-cube network

consisting of 2x2 cross-bar switching elements.

Separate networks are used to interconnect the instruction/data and the block transfer

busses in different clusters. The adopted network topology provides the Multiplus

architecture with two very desirable features: modularity and partitionability. Modularity

enables the Multiplus architecture to grow in numbers of clusters through a simple

addition of extra switching elements to the network. No re-wiring of the interconnections

between the elements already present in the network is required in such

operations. The

partitioning feature of the network provides the Multiplus architecture with the

possibility of supporting several independent or loosely-coupled groups of clusters. In

fact, the network ensures that it is possible to choose groups of clusters such that the

communication within a group does not interfere with the communication within any other

group of clusters.

The Multiplus Multistage Interconnection Network can support up to 128 clusters. Each

communication path between switching elements in the network is unidirectional and nine

bits wide. The transmitted messages can have variable length up to a maximum of 128 bytes.

Wormhole routing is used in the network and a single bit of the destination address field

of the messages is examined by each stage of switching elements to direct the message to

the next stage.

Six message types are supported by the Multistage Interconnection Network:

Write, Read,

Write Reply, Read Reply, DMA and DMA Reply. Every message can have only a single source

and a single destination, therefore broadcast or multicast type messages are not currently

handled by the network.

A message can be seen as a sequence of packets consisting of eight data bits and one

parity bit. In general, a message has three basic sections: the header, the preamble and

the data. The header is four byte long and contains information on the destination

address, message size, message type and identification of the module that has generated

the message within the source cluster. The preamble contains an image of the 64-bit

address lines of the source cluster. It is only needed in Read, Write, DMA and DMA Reply

messages. Read and Write messages occur when a module within a cluster wants to

access a memory position belonging to another cluster. The Write Reply message is used to

tell the I/O Processor which has generated a block write operation that the last requested

write operation has been completed. The Read Reply message returns the requested data to

the processing element which had issued the corresponding Read message. A DMA message sets

the Multistage Interconnection Network to perform a block transfer of length up to 64

Kbytes from a region of memory within a given cluster to the local memory of the

processing element which issued the DMA request. The DMA Reply message uses the

Instruction Bus to transfer the requested data in blocks of 128 bytes between clusters. On

completion of the DMA Reply operation, the Network Interface interrupts the processing

element which issued the DMA request.

The architecture of the switching element of the Interconnection Network implements a

2x2 cross-bar switch with FIFO buffers assigned to each switch input. Each switching

element with the FIFO buffers has been implemented with a single EPLD.

The Network Interface interconnects the cluster bus systems to the Multistage

Interconnection Network and also performs the functions of bus arbiter and bus reset

generation. The Network Interface consists of two identical sections: one that deals with

the Instruction/Data Bus and another which deals with the Block Transfer Bus.

In addition, it has a DMA Controller which is programmed through the

Instruction/Data

Bus and performs data block transfers through the Block Transfer Bus. Within each

section,

the Network Interface consists of 8 modules: the bus interface module with a master and a

slave section, the FIFO memory for messages to be transmitted, the message transmission

module, a dual-port memory for received messages, the message reception module,

registers,

the bus arbiter and the logic for bus reset generation.

The implementation of the Network Interface has been carried out with 11 EPLDs, five

for each section and one for the DMA Controller. The five EPLDS in each section perform

the following functions: bus master; bus slave; message transmission control; message

reception control; storage of the status of the messages sent by the interface and

generation of the address of the memory for received messages.

The Master section of the Network Interface is activated when some remote Read, Write

or DMA message arrives at the Interface or when a Write Reply message is received. The

Slave section is activated either when a remote access is generated within the cluster or

when a Read Reply message is received. In the first case, the information on the requested

access is stored in the memory for messages to be transmitted for later processing. The

Read Reply message occurs because at some point a cluster module requested a remote read

operation to the Network Interface. As an immediate answer to this read request, the Slave

section sends an instruction for the cluster module to relinquish the use of the cluster

bus and retry the read operation later on. Hopefully, in the meantime, the Network

Interface has enough time to process the read request and get a Read Reply message as a

result. Therefore, when the cluster module retries the read operation, the Slave section

is able to send back the requested data to the cluster module. This approach avoids

blocking the cluster bus while the Network Interface gets the answer for a remote read

operation.

The Message Transmission Control module is responsible for taking messages byte by byte

out of the memory for messages to be transmitted, packing them and transmitting them

through the Interconnection Network. The Message Reception Control module receives the

messages coming from the Interconnection Network, stores them in the memory for received

messages and instructs the bus interface module to generate the appropriate cluster bus

access.

In addition to the EPLDs, a FIFO memory has been used to implement the

memories for the messages to be transmitted. This FIFO memory consists of two sections: a

64-bit wide data section and an 18-bit wide control section. The dual-port memories for

message reception consist of 64-bit words and are divided into three different regions.

The first one works as a FIFO for the received messages. The second one works as a RAM

which stores the replies to messages sent by modules within the local cluster and the

third one stores an address and access code table for the interrupt registers of all the

modules within the local cluster. From one port, this memory is accessed for the reception

of messages coming from the Network in 8-bit packets. From the other port, this memory is

connected to the corresponding 64-bit cluster bus and can be read by the master or slave

section of the Interface and written by the slave section or by the DMA